Product Summary

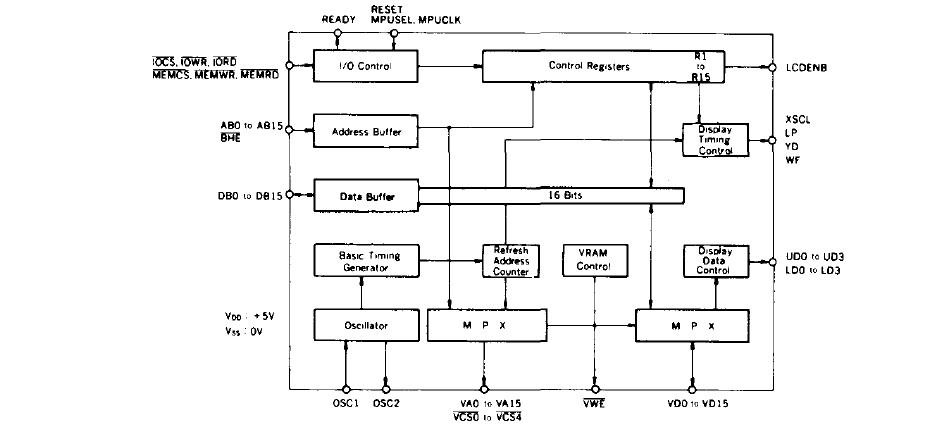

The SED1351FOA is a CMOS graphic LCD controller. The SED1351FOA is a high-duty dot matrix graphic display LCD controller. It can interface with an 8bits or 16bits MPU having a READY (WAIT) input pin. Cycle steal mode is used to have the MPU access the VRAM so that the display is not disturbed. The SED1351FOA contains circuits that control all data and addresses for cycle steal operations and requires no external data/address control circuit. Furthermore, the device has a chip select output pin for VRAM. This makes it possible to directly connect up to eight 64K SRAMs or two 256K SRAMs to the SED1351FOA without using an external decoder. The VRAM addresses are mapped in the MPU memory space. This feature enables the MPU to directly address any display data for efficient data manipulation especially when the user is drawing a picture. The SED1351FOA is available with two display modes to choose from, binary mode (on/off only) and gray mode (on/off and two gray steps). Use of the full 64K bytes capacity of VRAM makes it possible to display a maximum of 524.288 dots in the binary mode and 262.144 dots in the gray mode.

Parametrics

SED1351FOA absolute maximum ratings: (1)Supply voltage : Vss-0.3 to 7.0 V; (2)Input voltage: Vss-0.3 to VDD+0.3 V; (3)Output voltage : Vss-0.3 to VDD+0.3 V; (4)Output current/pin : ±10 mA; (5)Power dissipation : 200 mW; (6)Supply current : ±40 mA; (7)Storage temperature : -65 to 150 ℃.

Features

SED1351FOA features: (1)VRAM capacity: 64K bytes (Mapping : MPU memory space); (2)LCD display modes: Binary (ON/OFF only) Gray (ON/OFF+two gray steps); (3)LCD panel: 1-screen configuration (4bits or 8bits data transfer) 2-screen configuration (4bits data transfer for each display); (4)Maximum number of horizontal: 256 characters 2048 dots (Binary display mode) / 1024 dots (Gray display mode); (5)Maximum number of vertical lines •1.024 lines (1-screen drive) /2.048 lines (2-screen drive); (6)Panel division/OR function: Either to be selected in 1-screen drive mode; (7)Interface with MPU through use of READY (WAIT) signal; (8)Capability of using virtual display panel; (9)Smooth vertical scrolling; (10)Chip select output for VRAM; (11)Single power supply: 5V±10%; (12)Package: 100pin QFP (Plastic).

Diagrams

|

SED10HB45 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

SED10HE45 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

SED110LB30 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

SED110LE30 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

SED1180 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

SED1180F |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))